内含工程文件可以直接运行,且有仿真文件可以直接运行仿真看波形。文件中有文档讲解和程序注释也可以参考理解。

”fpga开发 axi4“ 的搜索结果

FPGA中AXI总线协议

FPGA——AXI4总线详解

标签: fpga开发

针对Xilinx KintexUltrascale系列FPGA 的PCIeXDMA在 AXI4-Stream接口形式下性能进行测试演示,支持4通道C2H/H2C、中断、轮询模式

基于FPGA的AXI4总线时序设计与实现.pdf

FPGA-AXI4总线介绍

标签: fpga开发

AXI协议概述,理解AXI4端口信号定义,如何理解归纳

fpga axi-can ip核数据手册

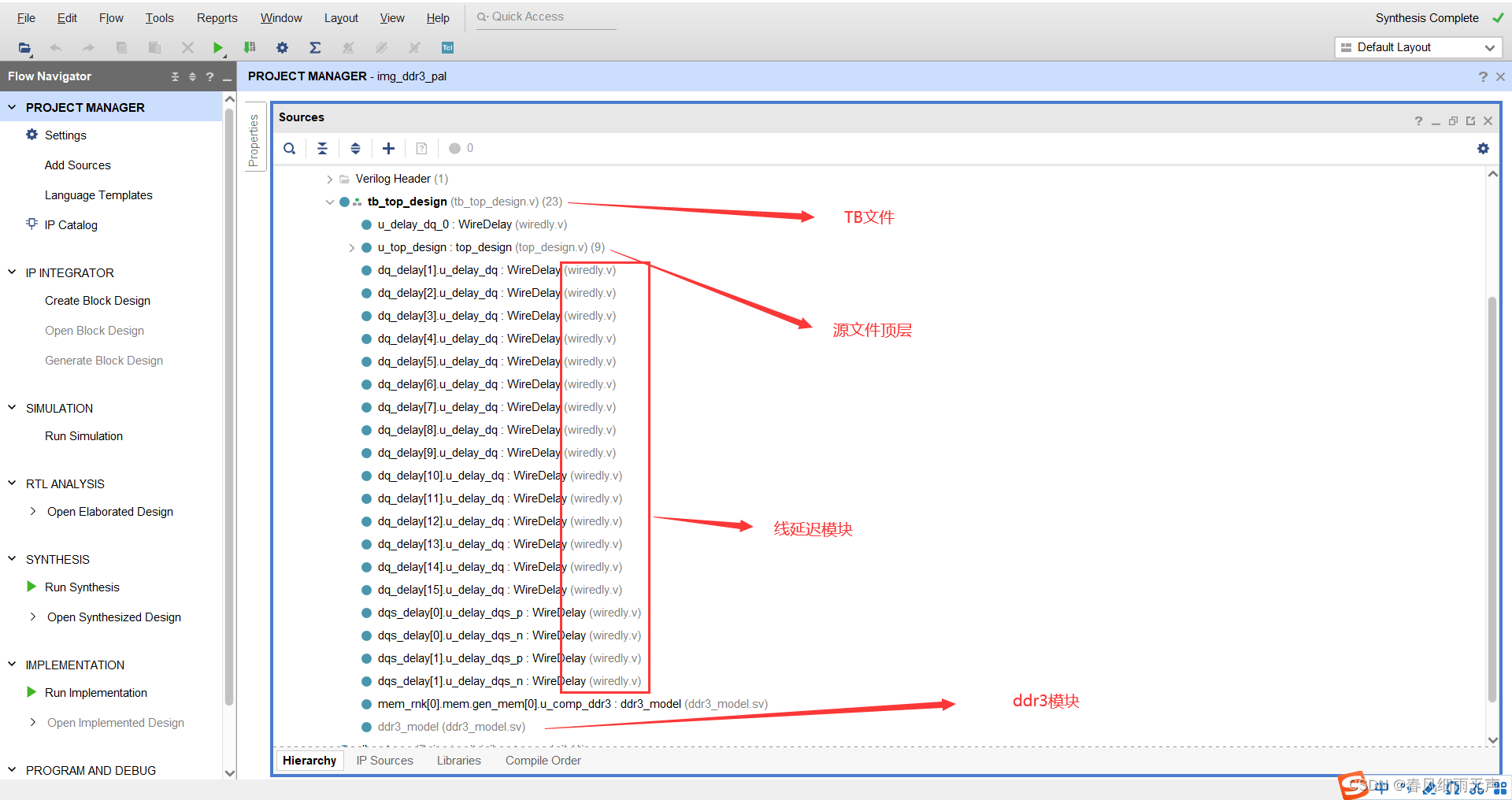

基于Xilinx FPGA的AXI接口多通道DDR4读写控制模块l逻辑Vivado2018.2 工程源码,实现4个独立的DDR4读写通道,通道数可由参数配置。

PS提供了供FPGA读写的AXI-HP接口用于两者的高速通信和数据交互。一般的,我们会采用AXI DMA的方式去传输数据,DMA代码基本是是C编写,对于FPGA开发者来说不利于维护和debug。本文提供一种手写AXI_MASTER接口用于PL ...

FPGA_AXI4总线

标签: AXI4

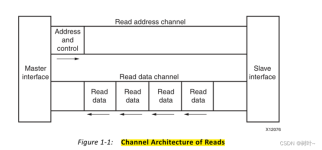

(一)AXI总线是什么? AXI是ARM 1996年提出的微控制器总线家族AMBA中的一部分。AXI的第一个版本出现在AMBA3.0,发布于2003年。当前的最新的版本发布于2010年。 AXI4:主要面向高性能地址映射... AXI4-Lite...

FPGA XC7A35T驱动程序,Microblaze实现。 项目程序可直接编译运行~

AXI4-Stream总线的FPGA视频系统的开发研究.pdf

FPGA AXI接口协议详解,并实现数据读写

FPGA控制DDR读写

通道信号源信号描述全局信号aclk主机全局时钟aresetn主机全局复位,低有效写通道地址与控制信号通道主机写地址ID,用来标志一组写信号主机写地址,给出一次写突发传输的写地址主机突发长度,给出突发传输的次数主机...

是一种高性能的随机存储器,...最初版本是AXI3,用于PS内部互联(使用的是AXI3),在2010年AXI3的基础上升级为AXI4。(PS端开发流程)系列PS端使用的是ARM公司的硬核CPU,内部使用的是ARM公司的。下图是ZYNQ-7000系列中。

FPGA中axi详解 及接口的中文意思

AXI总线目前已经发展到AXI5,在FPGA平台上常用的是AXI4。AXI4(AXI4-Full):满足高性能内存映射需求。支持256长度突发(burst)传输。AXI4-Lite:对于简单的、低吞吐量的内存映射通信。突发长度只能为1,数据位宽只...

在本文中,我们将探讨如何使用FPGA开发一个支持PCIe高速传输的PCIE AXI(Advanced eXtensible Interface)桥接器,并提供相应的源代码。总之,通过使用FPGA开发一个支持PCIe高速传输的PCIE AXI桥接器,您可以实现与...

XILINX FPGA AXI开发 参考文档

推荐文章

- Android RIL框架分析-程序员宅基地

- Python编程基础:第六节 math包的基础使用Math Functions_ps math function-程序员宅基地

- canal异常 Could not find first log file name in binary log index file_canal could not find first log file name in binary-程序员宅基地

- 【练习】生成10个1到20之间的不重复的随机数并降序输出-程序员宅基地

- linux系统扩展名大全,Linux系统文件扩展名学习-程序员宅基地

- WPF TabControl 滚动选项卡_wpf 使用tabcontrol如何给切换的页面增加滚动条-程序员宅基地

- Apache Jmeter常用插件下载及安装及软硬件性能指标_jmeter插件下载-程序员宅基地

- SpringBoot 2.X整合Mybatis_springboot2.1.5整合mybatis不需要配置mapper-locations-程序员宅基地

- ios刷android8.0,颤抖吧 iOS, Android 8.0正式发布!-程序员宅基地

- 【halcon】C# halcon 内存暴增_halcon 读二维码占内存-程序员宅基地